凡是在时钟信号作用下逻辑功能符合表1所示特性表所规定的逻辑功能者,就叫做D触发器。

| 表1 D触发器的特性表 |

| D | Qn+1 |

| 0 | 0 |

| 1 | 1 |

D触发器的特性方程为

| (1) |

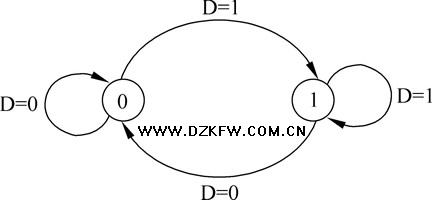

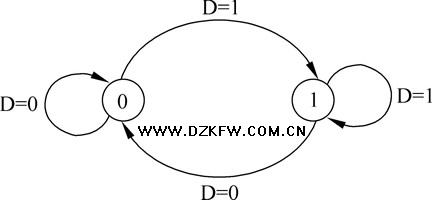

D触发器的状态转换图如图1所示。

|

| 图1 D触发器的状态转换图 |

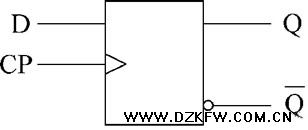

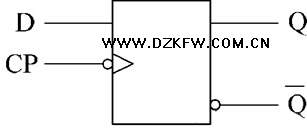

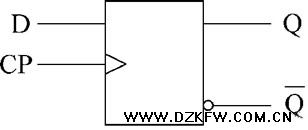

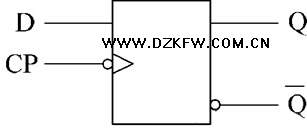

从表1可知,D触发器只有一个输入端D,其结构形式也有多种,图2所示为边沿型D触发器的逻辑图形符号,图2(a)所示为上升沿触发,图2(b)所示为下降沿触发。

|

|

| 图2(a) 上升沿触发 | 图2(b) 下降沿触发 |

凡是在时钟信号作用下逻辑功能符合表1所示特性表所规定的逻辑功能者,就叫做D触发器。

| 表1 D触发器的特性表 |

| D | Qn+1 |

| 0 | 0 |

| 1 | 1 |

D触发器的特性方程为

| (1) |

D触发器的状态转换图如图1所示。

|

| 图1 D触发器的状态转换图 |

从表1可知,D触发器只有一个输入端D,其结构形式也有多种,图2所示为边沿型D触发器的逻辑图形符号,图2(a)所示为上升沿触发,图2(b)所示为下降沿触发。

|

|

| 图2(a) 上升沿触发 | 图2(b) 下降沿触发 |